Volume-12, Issue-12, December 2023 JOURNAL OF COMPUTING TECHNOLOGIES (JCT) International Journal Page Number: 01-06

# A Low Area And High Speed VLSI Architecture of The Wavelet Filter For Image De-Noising:- A Review

Vaibhav Verma<sup>1</sup>, Prof. Amit Chauhan<sup>2</sup> <sup>1</sup>M.Tech Student, <sup>2</sup>Assistant Professor, <sup>1,2</sup>Department of Electronics and Communication, <sup>1,2</sup>, Vidhyapeeth Institute of Science & Technology (VIST), RGPV, Bhopal, INDIA

Abstract—The discrete wavelet transform has a huge number of applications in science, engineering, and mathematics and computer science. In numerical analysis and functional analysis, a discrete wavelet transform (DWT) is any wavelet transform for which the wavelets are discretely sampled. Practical applications can also be found in signal processing of accelerations for wavelet filter in digital communication and many others. Daub-6 derives is a wavelet filter bank operation. The proposed algorithm optimizes the wavelet filter bank architecture. This research analyzes the performance of orthogonal wavelet filters for image compression on variety of test images. The test images are of different size and resolution. The compression performance is measured, objectively peak signal to noise ratio and subjectively visual quality of image and it is found that orthogonal wavelets outperform. Under normal conditions, the DWT provides near perfect performance.

Keywords —Image Processor, filter wavelets, VLSI, MATLAB and Xilinx 14.7.

# I. INTRODUCTION

A. VLSI In Image Processing Faster computing is required than is achievable with the standard serial computer in order to create and deploy systems for robot vision and remote surveillance, faster computation is needed than is possible with the ordinary serial computer. This is because these types of tasks require real-time processing of images and an understanding of the scenes they depict. The development of very large scale integration (VLSI) has made it possible to examine more specialised processing architectures. These designs are intended to accommodate enormous data rates while keeping systems small and reasonably inexpensive. Both the utilisation of programmable processor arrays and the incorporation of individualized image processing algorithms onto silicon are presented and considered as

potential methods. Interpolation or scaling of digital images is a topic that has been getting a lot of interest as of late for several reasons. Picture scaling is the act of resizing a digital image, and it is a nontrivial operation that includes a tradeoff between efficiency, smoothness, and sharpness. This is because image scaling entails resizing the pixels that make up the image. These days, the image scalar is extensively used in a variety of portable medical devices, digital electronic equipment, digital cameras, digital picture frames, mobile phones, touch panel computers, and other similar products. The design of a low-cost, high-quality, and highperformance image scalar for multimedia devices using the VLSI technology has developed into a key trend in recent years. The requirement for and relevance of image scaling are becoming more and more apparent as the graphic and video applications available on mobile cell devices continue to develop and expand. Linear and nonlinear interpolation techniques are the two primary categories that make up the picture scaling algorithms that are based on interpolation. The simplest form of linear interpolation is a low-complexity algorithm called a closest neighbour algorithm. Nevertheless, this approach produces scaled pictures with blocking and aliasing art effects as a consequence of its use. The bilinear interpolation technique is the way of scaling that is used the most often. This approach allows the target pixel to be reached by using the linear interpolation model in both the horizontal and vertical dimensions. The bi-cubic interpolation algorithm is yet another well-known polynomial-based approach. This technique employs an extended cubic model to obtain the target pixel by means of a 2D regular grid. When compared to linear methods, result in a significant improvement in image quality. This is accomplished by a reduction in the effects of blocking, aliasing, and blurring...

# **B.** Image Processing

### The Image Preprocessing Steps

**Scaling-** The goal of the method known as magnification, which is a subset of the scaling approach, is to get a better

look at something by enlarging it, sometimes known as zooming in on it. During the process of reduction, we will be able to lower the amount of the data down to a level that is more manageable. Techniques such as linear or cubic convolution are used when resampling a picture. Nearest Neighborhood is also an option.

#### C. Image Reconstruction from Projections

Image reconstruction from projections is a subcategory of image restoration issues. In this kind of problem, an object with dimensions of two or more is rebuilt from a series of projections that only have one dimension. Each projection is created by passing a parallel beam of X-rays or any other kind of penetrating radiation through the item being seen. While observing the thing from a variety of perspectives, it is possible to acquire planar projections of the object. The reconstruction algorithms provide a picture of a thin axial slice of the item, which provides a glimpse of the object's inside that would be impossible to get without invasive surgical procedures. These methods are essential in a variety of fields, including medical imaging (CT scanners), astronomy, radar imaging, geological exploration, and the nondestructive testing of assembly components.

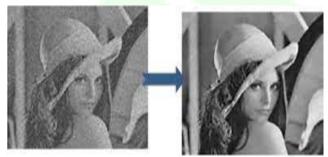

Fig. 1: Leena image (a) Noisy (b) Denoised

#### D. Digital Filter

In the field of signal processing, a digital filter is a kind of system that, in order to minimise or enhance certain features of a sampled, discrete-time signal, it applies mathematical operations on the signal in question. In contrast to this, the second primary form of electronic filter is an analogue filter, which is often an electronic circuit that operates on continuous-time analogue signals. This filter operates in a completely different manner from the digital filter.

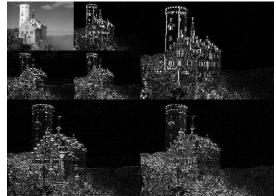

**Fig.2: Digital Filtering**

Digital filters are ubiquitous and an essential component of several consumer devices, including radios, mobile phones, and audio/video receivers, amongst others.

The digital filter is implemented by programme instructions (also known as software), which execute on the microprocessor. These instructions conduct the required mathematical operations on the data that were received from the ADC. An application-specific integrated circuit (ASIC) or field-programmable gate array (FPGA) may be used in place of a general-purpose microprocessor or a specialised digital signal processor (DSP) with a specific paralleled architecture in order to expedite operations such as filtering in certain high-performance applications.

#### E. Discrete wavelet transform

In comparison to other wavelet transforms, the main benefit it has over the Fourier transform is its superior temporal resolution, meaning that it is able to collect information about both frequency and position (location in time).

#### F. Haar wavelets

Alfréd Haar, a Hungarian mathematician, is credited with developing the DWT for the first time. The Haar wavelet transform may be thought of as simply pairing together input values, storing the difference between them, and sending on the total. This applies to an input that is represented by a list of integers. This procedure is carried out in a recursive manner, with the sums being paired off in order to give the subsequent scale. This ultimately leads to differences and a single concluding sum.

#### G. Daubechies Wavelets

In 1988, the Belgian mathematician Ingrid Daubechies devised a set of discrete wavelet transformations that has since become the industry standard. The scale of each resolution is twice that of the preceding scale. A family of wavelets is derived by Daubechies in her foundational work, with the Haar wavelet serving as the progenitor of the group.

#### H. Dual-Tree Complex Wavelet Transform (CWT)

CWT is an upgrade to the DWT that was developed relatively recently. It has crucial new features, including the following: It almost never changes shape and is directionally selective in two dimensions and higher. This is accomplished with a redundancy factor that is only significantly lower than the DWT before it was decimated. The non-separable M-D dual-tree CWT is built on a separable filter bank that is computationally efficient. Nevertheless, the M-D dual-tree CWT cannot be separated (FB).

#### I. Properties

It captures the temporal content, which is the times at which these frequencies occur. This can be done in two ways: first, it can be done in operations; second, it captures both concepts simultaneously. As a result of the combination of these two characteristics, the Fast Wavelet Transform, often known as the FWT, is an alternative to the more common Fast Fourier Transform (FFT).

# J. Time Issues

Since the filter bank contains rate-change operators, the discrete WT is not time-invariant and is, in fact, quite sensitive to the alignment of the signal in time. Mallat and Zhong came up with a novel approach for the wavelet representation of a signal that is invariant to time shifts as a solution to the time-varying issue that is associated with wavelet transformations. The sole parameter that is sampled along the dyadic sequence 2j (jZ) in accordance with this technique, which is referred to as a TI-DWT, is the scale parameter, and the wavelet transform is computed at each point in time.

# **II. LITERATURE REVIEW**

C. Y. Lien, et al.[1] In this work, we offer a simple hardware implementation of the bilateral filter for fast, cheap image processing. The use of multipliers may be reduced by 48% when using a method based on distanceoriented grouping and hardware resource sharing. Moreover, a powerful quantization technique is used to cut down on the size of necessary look up tables. The testing results demonstrate the effectiveness of the suggested design in saving money without sacrificing performance metrics like picture quality, frame rate, or operating clock frequency.

M. Mody et al.[2] Due to its edge-preserving characteristic, bilateral (BL) filtering is quickly replacing traditional noise filters in computer vision and analytics processing systems. Direct implementation of - Bilateral filtering is discussed in the literature; however this approach has a greater computing cost and can only be used in standalone applications. In order to increase the throughput of hardware IP in 16nm FinFET, this study provides a revolutionary method to Bilateral filtering by significantly reducing its complexity. The work provides many innovations, including a content-adaptive algorithm for Bilateral Filtering, a mixed-mode 1D Division LUT, and a space- and amplitude-quantized Fixed point 2D-LUT. The provided approach is also adaptable, allowing for the use of Octave scaling for picture pyramid construction and a general 2D convolution engine in computer vision applications. As compared to direct implantation, the suggested approach only needs 1/80 as much 2D LUT. When compared to a PC-based floating reference, the picture quality results reveal only a very little variance in pixels for the noise filtering output (between 1 and 3 pixels rms).

*C. Saranya et al.*[3] Advances in electronic technology are having an effect on the overall design framework, which creates a variety of problems for digital systems. VLSI-based image filter designs are crucial in telecommunications, image processing, and multimedia. Many VLSI-based systems have filter design errors in the

floating-point arithmetic stages due to issues with largesized components. The problem with the VLSI architecture is the lengthened component list of the filter design. The picture filtering method is often used for noise elimination. For low power embedded real-time image filtering applications, there is a growing need for performancebased hardware sorting algorithms. The transmission process typically causes a picture to become distorted due to noise. Denoising is a method for cleaning up noisy signals without losing potentially useful information. Distance matrix and hardware resource sharing approaches allow for much less multiplier use compared to the traditional approach. The suggested VLSI design for the bilateral filter has the potential to be more efficient than the current method.

S. D. Palekar et al.[4] For use in blood testing, a comprehensive biochemical sensing platform is created. One component of blood biochemical analysis is the use of enzymatic reaction with a reagent to generate a colorimetric variation of solutions. The created platform is centred on supplanting the physical optical filter wheel assembly with software-based wavelength filtering, thereby mitigating the hardware dependencies of current analyzers. The designed image capture platform and the softwarebased wavelength filtering unit are used in the studies to detect these differences. Using the dataset acquired by experimental means, the machine learning technique is employed to train the system to predict unknown concentrations. Blood glucose, albumin, and cholesterol were all sensed across a linear range from 10 to 400 mg/dL, 1 to 8 g/dL, and 10 to 800 mg/dL, respectively, with a limit of detection (LOD) of 2.8 mg/dL, 0.64 g/dL, and 3.14 mg/dL, respectively, to ensure the platform's viability. Consistent with the findings from a commercial biochemistry analyzer, this study found similar outcomes. Extensive testing reveals that the developed blood sensing platform is robust, portable, and accurate because of the reduction of hardware moving parts, and that it provides extreme operational flexibility thanks to software solutions, allowing for a wide variety of all-in-one instruments for blood analysis.

R. Karthickkeyan, A. K., et al.[5] The ubiquitousness of finite impulse response (FIR) filters in digital signal processing is attested to by their prevalence in domains as diverse as digital audio, picture processing, data transfer, the biological sciences, and many others. The FIR filter circuit has to support both high and low sample rates, as well as low power consumption, in order to be useful in a variety of contexts. Both conditions must be present at the same time. These two conditions are mutually exclusive and must be fulfilled. It takes a lot of multiplications to design and implement FIR filters, which wastes a lot of room and power. Reducing power consumption and making the most efficient use of available space are two of the primary goals of every DSP processor's design and implementation. The building pieces of a Finite Impulse Response (FIR) Filter are arithmetic and logical operations:

an adder, a flip-flop, and a multiplier. The FIR filter has a significant effect on the output and is responsible for the slowest frame rate. Both the queue and the field lengthened. The FIR Filter's low voltage and low power requirements make it amenable to development for VLSI applications. The booth multiplier's decreased latency and working speed, together with its already low power consumption, make this achievable. In this study, we introduce the Finite Impulse Response Filter and compare the two top-tier FIR filters by exploring its performance over a range of settings. These two jobs need the use of two different multipliers, the Array Multiplier and the Booth Multiplier.

According to P. T. L. Pereira et al. [6], effective Kalman filter (KF) designs are needed for real-time mobile applications like guiding nano-drones, localising robots, controlling the orbit of spacecrafts, pinpointing their locations using global positioning systems, identifying objects in photos, and fusing data from multiple sensors. The KF requires a lot of processing power since it is a kernel built from a series of sophisticated matrix operations, such as multiplications and inversions. The Kalman gain (KG) function is the most complicated building element in the KF since it inverts matrices at each iteration by using the determinant matrix and division. To achieve real-time KF processing, balancing competing low-power and high-performance needs is a significant design challenge for which we integrate architectural solutions of various sorts in this article. In this work, we describe the results of an investigation into several architectural forms, and we discover that semiparallel and sequential KF designs provide the optimal trade-offs between circuit area size, power dissipation, and processing performance. Our KF design is more efficient than current best practises because it uses 3.3 times less clock cycles and 2.8 times fewer arithmetic operations. Simulations of system identification, noise cancellation, and state estimation applications demonstrate the developed KF's utility in DSP. Results of the KF architecture are highlighted in the figures below, which show the speed of adaptation for system identification applications with a root mean square error (RMSE) of 0.01 after 12 samples, the precision level in noise elimination applications with an RMSE of 0.13, and the reliability in state estimation processes with an RMSE of less than 10% of system peak response.

*L-S. Joe et al.,[7]* Recent CMOS image sensors' widespread use of sub-micron pixels has allowed for the implementation of high-resolution cameras in compact form factors, such as thin mobile-phones. Customers expect improved picture quality even when pixel sizes decrease, therefore manufacturers must maintain or improve upon prior generations' pixel performance. A metal grid is often employed as an isolation structure between neighbouring colour filters to reduce optical interference between pixels. Nevertheless, when pixel sizes continue to decrease into the sub-micron zone, optical loss

rises owing to light absorption in the metal grid, which does not scale down with decreasing pixel size due to the diffraction limit. We have successfully shown a novel lossless, dielectric-only grid method. As a consequence, the Y-SNR is +1.2 dB better than the prior hybrid metal-and-dielectric grid, and the sensitivity is up 29%.

A. Yang, et al. [8] Ultrasound medical imaging is frequently utilised in clinic because it is a non-invasive, real-time, low-cost, and user-friendly alternative to classic lamp-house irradiation-based imaging technologies. Distinguishing between healthy and diseased tissue may be challenging using ultrasonic imaging due to the speckle noise inherent to the technology. After analysing speckle noise and the general filter, a novel approach for the medical ultrasonic imaging filter is presented; this is then validated experimentally. This is how we did our experiments: After distorting the original with Rayleigh noise, we use a median filter and an adaptive median filter to remove the noise. Once the picture has been processed with an adaptive median filter, the morphological filter is used to boost contrast and improve image quality. After denoising and analysing the photos, we compare the three noise filtering techniques. The findings also show that the novel approach is better than the alternatives.

Y. Mishra et al., [9] In the process of transmitting a signal to a receiver, noise is introduced, which leads to a number of miscommunications. In order to solve this issue, a novel window function for FIR filter design has been considered. The work presented here details the process through which we suggested a new window function to replace the traditional windowing approach. The spectrum qualities of the suggested window function, which is built from a concatenation of trigonometric functions, make it customizable in nature and form, and this is commonly done in order to make the function more in line with the requirements of the application. The simulation result displays the FIR low pass filter output after applying the supplied window function to a signal. Main-lobe width, Side-lobe roll off ratio, and Ripple ratio are only a few of the spectral properties of the suggested window function that are investigated. They have been compared to other window functions, including as the Kaiser, Hamming, Tukey, and Gaussian distributions, in terms of their spectral feature. Their simulation results confirmed that the suggested window function improved the signal-to-noise ratio and spectrum properties over the opposing existing window function.

W. He and et al., [10] In adaptable embedded computer vision applications, real-time object tracking is a must. In order to accomplish this, a low-cost high-speed VLSI system is proposed for object tracking, with features derived from unified textural and dynamic compressive sensing that are both computationally simple and robust, as well as elliptic matching that can update its templates quickly in real-time. For high frame rate with low hardware requirements, the system implements a memory-centric

architectural paradigm, multi-level pipelines, and parallel processing circuits. We have built a working FPGA model of the intended VLSI tracking system. The prototype achieves over 600 frames/s processing performance at 320x240 resolution and strong tracking results at a 100 MHz clock frequency.

#### III. PROBLEM FORMULATION AND OBJECTIVES

Non-linearities in the components do not affect digital filters in the same way that they do analogue filters, which makes the design of digital filters much simpler. The electrical components that make up an analogue filter are not flawless; their values are set to a limit tolerance (for example, resistor values often have a tolerance of 5%), and those values are subject to fluctuate depending on temperature and may drift over the course of time. The impact of variable component faults is substantially increased when the order of an analogue filter, and therefore its component count, grows. [Case in point:] an analogue filter with three orders. Since the coefficient values in digital filters are saved in the memory of the computer, these filters are far more reliable and accurate. In signal processing, one of the most important steps is called filtering, and its purpose is to remove undesired signals and noise from the source signal. Filters are used to distinguish between frequencies that carry relevant information and those that do not.

#### VI. CONCLUSION

This work proposes a VLSI filter implementation for image denoising with performance optimization. The orthogonal filter with discrete wavelet transform (DWT) is used as a tool for generating feature points and encoding procedure in this work. We investigate DWT as a method for encoding the feature points and IDWT as a method for decoding the feature points. The rebuilt picture is produced using an inverted version of the Feature transform. The filter architecture to change the filter section in needed wavelet transforms and to optimise the filter bank section in the suggested design were both parts of the filter architecture. The transform function, which is intended to make the image processing approach more effective. The primary emphasis of this study was placed on the processing of images using FPGA technology. All of these objectives are to be accomplished by optimising the filter and transform architecture. In most cases, we use DWT transformations in order to carry out a comparative examination of various picture compression methods. Each method comes with its own set of advantages and disadvantages. When viewed from the point of view of maintaining a good picture quality on the rebuilt image.

# REFERENCES

[1] C. Y. Lien, C. - H. Tang, P. - Y. Chen, Y. - T. Kuo and Y. - L. Deng, "A Minimal expense VLSI Engineering of the Two-sided Channel for Continuous Picture Denoising," in IEEE Access, vol. 8, pp. 64278-64283, 2020,

- [2] M. Mody, R. Allu, J. Villarreal, W. Wallace, N. Nandan and A. Baranwal, "High Throughput VLSI Engineering for Two-sided Sifting in PC Vision," 2022 IEEE Worldwide Meeting on Gadgets, Registering and Correspondence Advances (CONECCT), Bangalore, India, 2022, pp. 1-4,

- [3] C. Saranya, M. V. Vijayananth, S. Mouleeshwaran and D. Kaviyarasu, "A Picture Handling Application: Plan of VLSI based Reciprocal Channel utilizing Distance Grid Technique," 2022 Second Worldwide Meeting on Trend setting innovations in Savvy Control, Climate, Processing and Correspondence Designing (ICATIECE), Bangalore, India, 2022, pp. 1-5,

- [4] S. D. Palekar, J. Kalambe and R. M. Patrikar, "Biochemical Blood Detecting Stage With CMOS Picture Sensor and Programming Based Frequency Channel," in IEEE Sensors Diary, vol. 22, no. 22, pp. 21753-21760, 15 Nov.15, 2022,

- [5] K, R. Karthickkeyan, S. Kishore and R. Sharan, "Stall Multiplier-Based Strong Model of FIR Channels for VLSI Applications," 2022 sixth Worldwide Gathering on Hardware, Correspondence and Aviation Innovation, Coimbatore, India, 2022, pp. 249-254, doi: 10.1109/ICECA55336.2022.10009401.

- [6] P. T. L. Pereira, G. Paim, P. Ü. L. d. Costa, E. A. C. d. Costa, S. J. M. de Almeida and S. Bampi, "Building Investigation for Energy-Proficient Fixed-Point Kalman Channel VLSI Plan," in IEEE Exchanges for Extremely Huge Scope Reconciliation (VLSI) Frameworks, vol. 29, no. 7, pp. 1402-1415, July 2021,

- [7] I. -S. Joe et al., "Improvement of Cutting edge Between Variety Channel Framework on Sub-Micron-Pixel CMOS Picture Sensor for Portable Cameras with High Responsiveness and High Goal," 2021 Discussion on VLSI Innovation, Kyoto, Japan, 2021, pp. 1-2.

- [8] A. Yang, "Research on image filtering method to combine mathematics morphology with adaptive median filter," 9th International Conference on Optical Communications and Networks, Nanjing, 2021, pp. 55-59, doi: 10.1049/cp.2021.1152.

- [9] Y. Mishra and R. Rastogi, "Plan of FIR Channel utilizing New Window Capability to eliminate Boisterous Sign," 2021 third Global Gathering on Advances in Processing, Correspondence Control and Systems administration (ICAC3N), More noteworthy Noida, India, 2021, pp. 1011-1017.

- [10] W. He et al., "A Minimal expense Rapid Item Following VLSI Framework In light of Bound together Textural and Dynamic Compressive Highlights," in IEEE Exchanges on Circuits and Frameworks II: Express Briefs, vol. 68, no. 3, pp. 1013-1017, Walk 2021,